# **Flying Probe Guidelines**

# **Revision Record**

| Revision | Date            | Approval      | Originator       |

|----------|-----------------|---------------|------------------|

| С        | 22-Oct-2015     | Kevin Schmitt | Stephen Whitaker |

| В        | 1-December-2011 |               | Steve Hoover     |

| A        | 12-June-2006    |               | Jim Arient       |

|          |                 |               | Steve Hoover     |

A flying probe tester can perform many of the same tests that are provided with Incircuit Test (ICT) using bed-of-nails fixturing. The flying probe tester is a fixtureless tester that utilizes several moving arms with test probes to access the test points on a PC board. Typically, the PC board is placed upside down in the tester, and multiple arms with test probes move across the bottom side of the board, touching down on test points and taking measurements. The biggest advantage of this test is that it does not usually require a test fixture. The greatest limitation is that it has long test times due to the arm movements. Below is a list of guidelines for board design that will optimize flying probe testing.

### **GUIDELINE #FP-1:** Test Point Guidelines for use with Flying Probe Testers

Test Points should follow the same basic rules as described in our guidelines for ICT bed-of-nails fixtures. Most through-hole components can be probed with the flying probe technique, as long as the leads are not too long which creates a steep solder joint. The leads must be free of pin-in-paste residue, and it is desirable to probe a lead that is not longer than the diameter of the pad through which it is protruding. Surface mount pads can be used as test points; however, we recommend not relying on fine pitch ICs for access.

Most of the test points should be accessible from one side of the PCB there should multiple test points for power and ground on both sides of the PCB. Since the flying probe can only access one side of the PCB at a time, a test of the top-side test points and bottom-side test points will have an isolated fault spectrum, resulting in potentially missed shorts and component tests.

When checking accessibility and selecting test points, some targets are preferred over others.

<u>Preferred:</u> Test pads, SMD pads, and vias. These targets should meet the restrictions outlined in guidelines below.

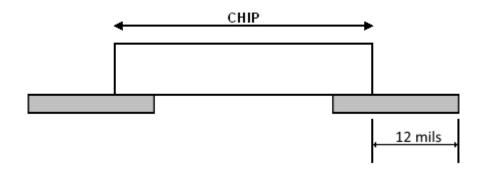

<u>Minimize:</u> Probing of the following items: IC pins, large vias or holes with small pad sizes (see guideline #3), through hole components with long pin lengths, SMD devices where the pin size is near the land size (SMD lands should extend out from the device a minimum of 12 mils past the worst case placement of the device lead.), and steep solder joints (see guideline #8).

Not available: Targets under 10 mils by 10 mils will not be probed.

## **GUIDELINE #FP-2:** Calculate the Keep-out Area

A keep-out area around components must be maintained so that the angled probes can access test points. The keep-out distance can be estimated for a component's height by utilizing the following equation, where PA = probe angle:

tan (PA) = (Keep-out Distance)/(Height of the Component)

Keep-out Distance = target size + [tan (PA) \* (Height of the Component)]

Factoring in a 15mil test target, for a 16 degree probe:

Keep-out Distance = 0.015" + (0.268 \* (height of the component))

## **GUIDELINE #FP-3:** Probing Large Via Holes / Large Holes

Large via holes can create problems when the needle-type test probes are used. If the hole is too large, the probe will actually bottom-out on hole contaminates and never make contact with the edges of the via barrel. To avoid this ensure that the annular ring is large enough to make contact. The pad diameter should be at least 20 mils larger than the drill size. This ensures that a 10 mil test target exists on the annular ring.

| Drill Size    | Pad Size                |  |

|---------------|-------------------------|--|

| Up to 14 mils | 20 mil minimum – 25 mil |  |

|               | preferred               |  |

| > 15 mils     | Drill size + 20 mils    |  |

# **GUIDELINE #FP-4:** Consider the Impact When Choosing Test Point Rules between Flying Probe and Bed-of-Nails

Occasionally a revision of a board may be built of a PC board that will never be considered for test using bed-of-nails fixtures. Flying probe testers can reliably hit smaller test points. The following test point rules can be used for boards intended to be tested ONLY with a flying probe tester and NOT by bed-of-nails fixtures.

Test pad diameter: 10mil (0.254 mm) minimum to 20mil (0.5 mm) recommended Test pad spacing: 16mil (0.4 mm) minimum to 33mil (0.84 mm) recommended

Note: With the use of a 25mil (0.64 mm) test point diameter and 40mil (1.02 mm) test points spacing, a bed-of-nails fixture can conceptually be made; but contact repeatability will be low with any volume, and the fixture will be very expensive.

# **GUIDELINE #FP-5:** Handling and Alignment Guidelines

The PC board in a flying probe is held on opposite edges by board clamps. These clamps are placed on the longest edges of the board to reduce board flex as the test points make contact. The clamps can access breakaways, but if this is not possible, an area of 0.120 in. (3.05 mm) should be left free of components and test points along the longest edges on top and bottom of the board.

\*Note: If this requirement cannot be met, a carrier may be quoted to hold the board in the tester.

Alignment / Board tooling pins are not used in flying probe testers. Optical cameras align the PC board using the board's fiducials. The same fiducials that the board assembly equipment used can be utilized, but they should be placed in opposite corners of the PC board. Use at least 2 fiducials. We recommend having a 10 to 20 mil solder mask relief around fiducials.

### **GUIDELINE #FP-6:** Panelized Boards

Panelized boards can be tested in the flying probe tester. Ideally the PCBs will have component free areas between them to allow for locating board flex standoff supports.

### **GUIDELINE #FP-7:** Optimize Flying Probe Test Times

Several things can be done to reduce the test time of the flying probe tester. Test time is directly linked to the movement of the test arms, and movement of the test arms is directly linked to the size of the PC board and number of test points.

By default, test time is reduced by optimizing the shorts testing to high percentage shorts by use of a proximity variable. Component pads within the range of the proximity variable are tested against each other for shorts.

Do not place large components on the bottom side of the board. The height of the largest bottom-side component causes the arms to move additional distance in the Z direction. Components with a height greater than 10 mm should be placed on the top.

Place connectors or large test points, greater than 45 mil (1.14 mm), on top of the PC board for power and ground nets. This will allow fixed resources to be placed on the bottom of the tester, so that they can continuously access these large nets. The time savings comes from the continual access of these nets. In some cases several hundred arm movements to access these nets can now be eliminated.

#### **GUIDELINE #FP-8:** Avoid probing steep solder joints Reducing witness marks

Probing a steep solder joint will cause the test probes to slide off of the intended target. Sliding probes can cause solder flakes and damage to the PCB. Many factors affect the angle of the solder joint such as the length, height and how much solder is applied. Preferred solder joints used as test targets should have a length to height ratio of at least 2 to 1. Also consider the amount of solder applied. The solder joint should level out near the edge of the pad to ensure that the probes don't slide off. On test targets with steep solder joints and small traces attached, consider using thicker traces or tapering the trace to create a wider area where the trace meets the component. This will prevent a sliding probe from significantly damaging the trace.

A Flying Probe DFT Analysis may be completed on a board if CAD files include accurate component outlines and heights.